## **DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING**

# **IC APPLICATIONS LABORATORY**

## STUDENT LABORATORY MANUAL

(As per 2021-2022 Academic Regulations)

B.E V SEMISTER E&CE SUBJECT CODE: PC 551 EC

Roll No.:\_\_\_\_

**DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING**

# **IC APPLICATIONS LABORATORY**

# STUDENT LABORATORY MANUAL

(As per 2021-2022 Academic Regulations)

B.E V SEMISTER E&CE SUBJECT CODE: PC 551 EC

# **Prepared by**

# Mr. P. Ramesh Babu, Assistant Professor Mr. D. Suresh, Assistant Professor

# Methodist College of Engineering & Technology

## DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING

| Experimen | Title of the Experiment | Date | Page | e Marks Re |   | Remarks/ |   |           |

|-----------|-------------------------|------|------|------------|---|----------|---|-----------|

| t No.     |                         |      | No.  | E          | 0 | R        | Τ | Signature |

|           |                         |      |      |            |   |          |   |           |

| 1         |                         |      |      |            |   |          |   |           |

| 2         |                         |      |      |            |   |          |   |           |

|           |                         |      |      |            |   |          |   |           |

| 3         |                         |      |      |            |   |          |   |           |

|           |                         |      |      |            |   |          |   |           |

| 4         |                         |      |      |            |   |          |   |           |

|           |                         |      |      |            |   |          |   |           |

| 5         |                         |      |      |            |   |          |   |           |

|           |                         |      |      |            |   |          |   |           |

| 6         |                         | 1    |      |            |   |          |   |           |

|           |                         |      |      |            |   |          |   |           |

| 8       Image: Ima |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 9     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10     10 <t< th=""><th></th></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

# COLLEGE OF ENGINEERING AND TECHNOLOGY

Approved by AICTE New Delhi | Affiliated to Osmania University, Hyderabad Abids, Hyderabad, Telangana, 500001

## **DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING**

## Vision of the Institute:

To produce ethical, socially conscious and innovative professionals who would contribute to sustainable technological development of the society.

## Mission of the Institute:

To impart quality engineering education with latest technological developments and interdisciplinary skills to make students succeed in professional practice

To encourage research culture among faculty and students by establishing state of art laboratories and exposing them to modern industrial and organizational practices

To inculcate humane qualities like environmental consciousness, leadership, social values, professional ethics and engage in independent and lifelong learning for sustainable contribution to the society

## Vision of the Department:

To strive to become centre of excellence in Education, Research with moral, ethical values and serve society

## **Mission of the Department:**

M1: To provide Electronics & Communication Engineering knowledge for successful career either in industry or research

M2: To develop Industry-Interaction for innovation, product oriented research and development.

M3: To facilitate value added education combined with hands-on trainings

## **Program Educational Objectives:**

PEO 1: Apply the knowledge of Basic sciences and Engineering in designing and implementing the solutions in emerging areas of Electronics and Communication Engineering.

PEO 2: Pursue the research or higher education and practise profession.

PEO 3: Adapt to the technological advancements for providing the sustainable Engineering solutions to meet organisation/society needs

PEO 4: Work as an individual or in a team with professional ethics and values.

## **DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING Program Outcomes:**

**1. Engineering knowledge:** Apply the knowledge of mathematics, science, engineering fundamentals, and an engineering specialization to the solution of complex engineering problems.

**2. Problem analysis:** Identify, formulate, review research literature, and analyze complex engineering problems reaching substantiated conclusions using first principles of mathematics, natural sciences, and engineering sciences.

**3. Design/development of solutions:** Design solutions for complex engineering problems and design system components or processes that meet the specified needs with appropriate consideration for the public health and safety, and the cultural, societal, and environmental considerations.

**4. Conduct investigations of complex problems:** Use research-based knowledge and research methods including design of experiments, analysis and interpretation of data, and synthesis of the information to provide valid conclusions.

**5. Modern tool usage:** Create, select, and apply appropriate techniques, resources, and modern engineering and IT tools including prediction and modeling to complex engineering activities with an understanding of the limitations.

**6.** The engineer and society: Apply reasoning informed by the contextual knowledge to assess societal, health, safety, legal and cultural issues and the consequent responsibilities relevant to the professional engineering practice.

**7. Environment and sustainability:** Understand the impact of the professional engineering solutions in societal and environmental contexts, and demonstrate the knowledge of, and need for sustainable development.

**8. Ethics:** Apply ethical principles and commit to professional ethics and responsibilities and norms of the engineering practice.

**9. Individual and team work:** Function effectively as an individual, and as a member or leader in diverse teams, and in multidisciplinary settings.

**10. Communication:** Communicate effectively on complex engineering activities with the engineering community and with society at large, such as, being able to comprehend and write effective reports and design documentation, make effective presentations, and give and receive clear instructions.

**11. Project management and finance:** Demonstrate knowledge and understanding of the engineering and management principles and apply these to one's own work, as a member and leader in a team, to manage projects and in multidisciplinary environments.

**12. Life-long learning:** Recognize the need for, and have the preparation and ability to engage in independent and life-long learning in the broadest context of technological change.

## Program Specific Outcomes (PSOs):

**PSO1: Professional Competence**: Apply the knowledge of Electronics & Communication Engineering principles in different domains like VLSI, Signal processing, Communication, Embedded system & Control Engineering.

**PSO2: Technical Skills**: Able to design and implement products using the cutting- edge software and hardware tools and hence provide simple solutions to complex problems.

**PSO3:** Social consciousness: Graduates will be able to demonstrate the leadership qualities and strive for the betterment of organization, environment and society

**METHODIST COLLEGE OF ENGINEERING AND TECHNOLOGY** Approved by AICTE New Delhi | Affiliated to Osmania University, Hyderabad

Abids, Hyderabad, Telangana, 500001

## **DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING**

## LAB INSTRUCTIONS

## Lab Rule of conduct, DO's & DON'Ts

Conduct yourself in a responsible manner at all times in the laboratory. Don't talk aloud or crack jokes in lab.

A lab coat should be worn during laboratory experiments.

Dress properly during a laboratory activity. Long hair, dangling jewellery and loose or baggy clothing are a hazard in the laboratory.

Observe good housekeeping practices. Replace the materials in proper place after work to keep the lab area tidy.

Do not wander around the room, distract other students, startle other students or interfere with the laboratory experiments of others.

Do not eat food, drink beverages or chew gum in the laboratory and do not use laboratory glassware as containers for food or beverages.

#### **Rules & Guidelines for conducting Lab-Work**

Students are not allowed to touch any equipment, in the laboratory area until you are instructed by Teacher or Technician.

Before starting Laboratory work follow all written and verbal instructions carefully. If you do not understand a direction or part of a procedure, ASK YOUR CONCERNED TEACHER BEFORE PROCEEDING WITH THE ACTIVITY.

Before use equipment must be read carefully Labels and instructions. Set up and use the equipment as directed by your teacher. If you do not understand how to use a piece of equipment, ASK THE TEACHER FOR HELP!

Perform only those experiments authorized by your teacher. Carefully follow all instructions, both written and oral. Unauthorized experiments are not allowed in the Laboratory. Students are not allowed to work in Laboratory alone or without presence of the teacher. Any failure / break-down of equipment must be reported to the teacher. Protect yourself from getting electric shock.

**METHODIST COLLEGE OF ENGINEERING AND TECHNOLOGY** Approved by AICTE New Delhi | Affiliated to Osmania University, Hyderabad

Abids, Hyderabad, Telangana, 500001

| Course Code      | Course Title           |   |   |         |     | Core/<br>Elective |         |

|------------------|------------------------|---|---|---------|-----|-------------------|---------|

| PC551EC          | IC APPLICATION         |   |   | NS LAB  |     | Core              |         |

| Prerequisite     | Contact Hours per Week |   |   | CIE SEE | SEE | E Credits         |         |

| LICA<br>PC 501EC | L                      | Т | D | Р       | CIL | BLL               | creatis |

| STLD<br>PC302EC  | -                      | - | - | 2       | 25  | 50                | 1       |

## **DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING**

## **Course Objectives:**

Design and analyze the various linear application of Op-amp.

Design and analyze the active filters circuit using Op-amp.

Design and analyze oscillators and Multivibrators using Op-amp & 555.

Design sequential circuits- Counters & Registers.

## **Course Outcomes:**

Implement operational amplifiers Linear & Non-linear circuits.

Implement Active filters using Op-amps.

Implement oscillators, Multivibrators, etc., using Op-amps.

Illustrate sequential circuits – Counters & Registers

## PART- A

- 1. Measurement of op-Amp. Parameters, Voltage follower.

- 2. Inverting and non- Inverting amplifiers using Op-Amp.

- 3. Integrator Differentiator circuits using Op-Amp.

- 4. Active filters: LP, HP and BP filters using Op-Amp.

- 5. Clipper and clamper circuit using Op-Amp.

- 6. Triangular wave generator using Op-Amp.

- 7. Monostable and Astable multivibrator using Op-Amp.

- 8. Monostable and Astable multivibrator using 555 Timer.

- 9. IC voltage regulator.

- 10. Voltage controlled oscillator NE 565

- 11. Four bit ADC and DAC using Op Amp

## PART - B

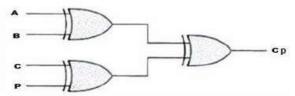

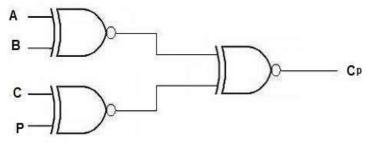

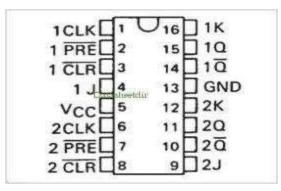

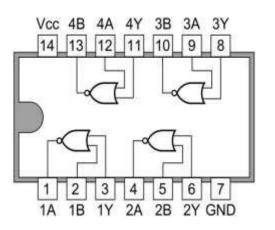

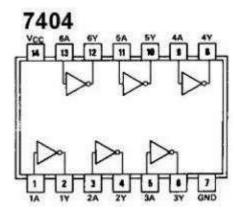

- 1. Flip Flop conversions and latches using gates and ICs.

- 2. Designing Synchronous, Asynchronous up/ down counters.

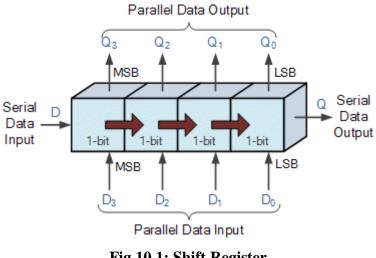

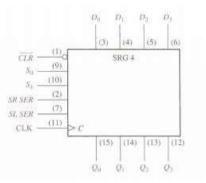

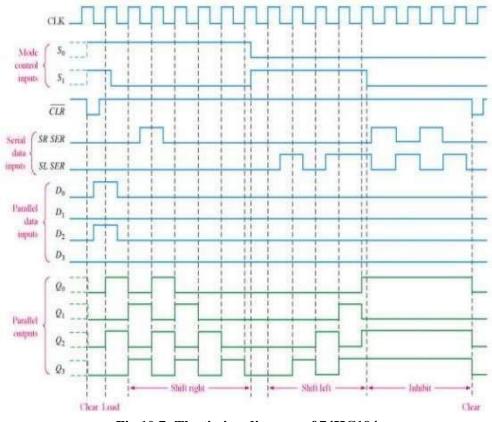

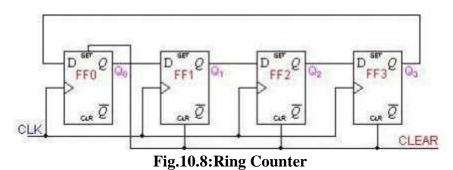

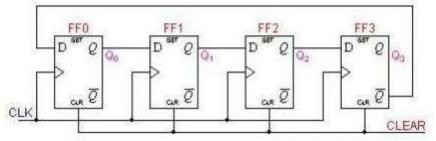

- 3. Shift Registers and Ring counters using IC Flip-Flop & Standards IC counters.

- 4. Interfacing counters with 7-segment LED /LCD display units.

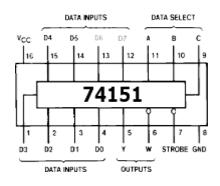

- 5. Mux Demux applications.

**Note:** Atleast ten experiments should be conducted in the semester, of which three should be from PART - B.

## Suggested Readings:

- 1. D.RoyChowdhary, B.JainShail Linear Integrated circuit, 4th Edition.

- 2. Jain R.P., "Modern Digital Electronics" 3/e TMH 2003.

# METHODIST

#### **COLLEGE OF ENGINEERING AND TECHNOLOGY**

Approved by AICTE New Delhi | Affiliated to Osmania University, Hyderabad Abids, Hyderabad, Telangana, 500001

## **DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING**

| Sl. No | Title of the Experiment               | Page No. |

|--------|---------------------------------------|----------|

|        | PART- A                               |          |

| 1      | a) Measurement of op-Amp. Parameters, | 6        |

|        | b) Voltage follower                   |          |

| 2      | a) Inverting amplifiers using Op-Amp  | 10       |

|    | b) Non- Inverting amplifiers using Op-Amp              |    |

|----|--------------------------------------------------------|----|

| 3  | a) Integrator using Op-Amp                             | 16 |

|    | b) Differentiator using Op-Amp                         |    |

| 4  | a) Low Pass filter using Op Amp                        | 23 |

|    | b) High Pass filter using Op Amp                       |    |

|    | c) Band Pass filter using Op Amp                       |    |

| 5  | Triangular wave generator using Op-Amp                 | 30 |

| 6  | a) Monostable multivibrator using 555 Timer            | 33 |

|    | b) Astable multivibrator using 555 Timer               |    |

|    | PART- B                                                |    |

| 7  | Flip Flop conversions and latches using gates and ICs  | 41 |

| 8  | Designing Synchronous, Asynchronous up/ down counters  | 46 |

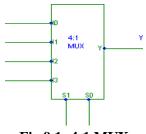

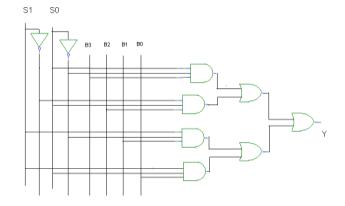

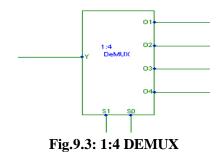

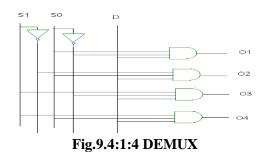

| 9  | Mux – Demux applications                               | 49 |

| 10 | Shift Registers and Ring counters using IC Flip-Flop & | 54 |

|    | Standards IC counters                                  |    |

|    | BEYOND SYLLABUS                                        |    |

| 11 | Code Converters and Parity Generator & Checker         | 60 |

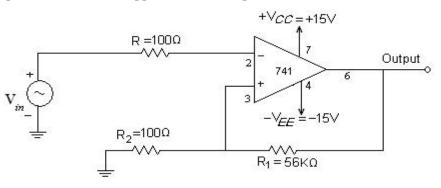

| 12 | Schmitt Trigger Circuits- using IC 741 & IC 555        | 69 |

|    |                                                        |    |

## **INTRODUCTION**

## IC 741 Op Amp Basics, Characteristics, Pin Configuration, Applications

## **Introduction to Operational Amplifiers**

An operational amplifier, also called as an op-amp or op amp, is an integrated circuit primarily designed for performing analogue computations. It has a very high voltage gain, typically of the order of 104 (100dB).

Although they are specially designed for performing operations like addition, subtraction, integration, differentiation etc., by using external components like resistors and capacitors to create a required feedback mechanism, it can also be used as an amplifier and for many other functions like filters, comparators etc.

Op-Amp IC's have become an integral part of almost all analogue circuitry. In this article we will take a look at one of the most used Op-Amp ICs: IC 741 Op Amp.

## IC 741 Op Amp (Operational Amplifier)

The 741 Op Amp IC is a monolithic integrated circuit, comprising of a general purpose Operational Amplifier. It was first manufactured by Fairchild semiconductors in the year 1963. The number 741 indicates that this operational amplifier IC has 7 functional pins, 4 pins capable of taking input and 1 output pin.

IC 741 Op Amp can provide high voltage gain and can be operated over a wide range of voltages, which makes it the best choice for use in integrators, summing amplifiers and general feedback applications. It also features short circuit protection and internal frequency compensation circuits built in it. This Op-amp IC comes in the following form factors:

## Pinout of IC 741 Op Amp and their Functions

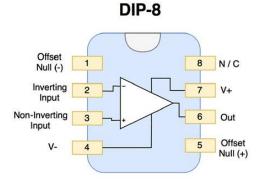

Fig. A illustrates the pin configurations and internal block diagram of IC 741 in 8 pin DIP package.

Fig. A: Pin Configuration of IC 741 Op Amp

**Pin4 & Pin7 (Power Supply):** Pin7 is the positive voltage supply terminal and Pin4 is the negative voltage supply terminal. The 741 IC draws in power for its operation from these pins. The voltage between these two pins can be anywhere between 5V and 18V.

**Pin6** (**Output**): This is the output pin of IC 741. The voltage at this pin depends on the signals at the input pins and the feedback mechanism used. If the output is said to be high, it means that voltage at the output is equal to positive supply voltage. Similarly, if the output is said to be low, it means that voltage at the output is equal to negative supply voltage.

**Pin2 & Pin3 (Input):** These are input pins for the IC. Pin2 is the inverting input and Pin3 is the non-inverting input. If the voltage at Pin2 is greater than the voltage at Pin3, i.e., the voltage at inverting input is higher, the output signal stays low. Similarly, if the voltage at Pin3 is greater than the voltage at Pin2, i.e., the voltage at non-inverting input is high, the output goes high.

**Pin1 & Pin5 (Offset Null):** Because of high gain provided by 741 Op-Amp, even slight differences in voltages at the inverting and non-inverting inputs, caused due to irregularities in manufacturing process or external disturbances, can influence the output. To nullify this effect, an offset voltage can be applied at pin1 and pin5, and is usually done using a potentiometer.

**Pin8** (N/C): This pin is not connected to any circuit inside 741 IC. It's just a dummy lead used to fill the void space in standard 8 pin packages.

## Specifications

The following are the basic specifications of IC 741:

Power Supply: Requires a Minimum voltage of 5V and can withstand up to 18V

**Input Impedance:** About  $2 M\Omega$

**Output impedance:** About 75  $\Omega$

Voltage Gain: 200,000 for low frequencies

Maximum Output Current: 20mA

**Recommended Output Load:** Greater than  $2 \text{ k}\Omega$

Input Offset: Ranges between 2mV and 6mV

**Slew Rate:** 0.5V/microsecond (It is the rate at which an Op-Amp can detect voltage changes) The high input impedance and very small output impedance makes IC 741 a near ideal voltage amplifier.

## Applications

Following are the applications of IC 741 Op Amp across different use cases:

**Amplifiers:** 741 IC is mostly used to amplify signals of varying frequencies ranging from DC to higher radio frequencies. It is also used in frequency selective amplifiers which filter out signals of unwanted frequencies, E.g. tone control systems in stereo and Hi Fi systems.

**Computational:** Many electronic circuits that perform mathematical operations like integration, differentiation, summers etc. use 741 Op-Amp.

**Rectifiers:** Ordinary diodes used in rectifiers have voltage drop across them which makes it unsuitable for high accuracy signal rectifiers. The 741 IC can be configured to perform as an ideal diode i.e., with no voltage drop at all and can be used in precise rectifier circuits.

**Oscillators:** Op-Amp IC 741 is used as an oscillator in function generators to create different output waveforms like sinusoidal, square, triangular etc. It is also used in Pulse Width Modulators (PWM generators)

**Comparators:** The 741 IC can be used to compare voltage signals and determine if they are almost of the same voltage. This can be used in voltage regulators and signal comparators.

**ADCs / DACs:** 741 Op-Amp can be used to create Digital to Analogue Converters that can take digital binary input from computers or microcontrollers and create a corresponding analogue signal. Similarly, it is can also used in Analogue to Digital circuits.

| The typical parameters of a 741 IC |                     |             |  |  |

|------------------------------------|---------------------|-------------|--|--|

| Parameters                         | Typical Range       | Ideal Value |  |  |

| Open Loop Gain(A)                  | $10^5$ to $10^8$    | x           |  |  |

| Input Resistance(R <sub>i</sub> )  | $10^5$ to $10^{13}$ | x           |  |  |

| Output Resistance(R <sub>o</sub> ) | 10 to 100           | 0           |  |  |

## IC 555 Timer Working: Pin Diagram & Specifications

The 555 timer IC is an integral part of electronics projects. Be it a simple project involving a single 8-bit micro-controller and some peripherals or a complex one involving system on chips (SoCs), 555 timer working is involved. These provide time delays, as an oscillator and as a flip-flop element among other applications.

Introduced in 1971 by the American company Signetics, the 555 is still in widespread use due to its low price, ease of use and stability.

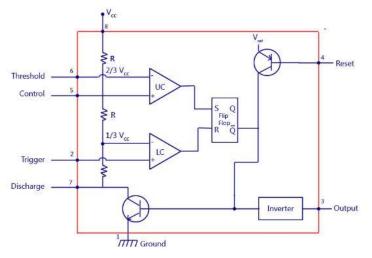

Fig. B shows the pin diagram of the timer IC 555 and Table A shows the description of the various pins of timer IC 555.

Fig. B: Pin Diagram of IC 555

|     | Table A: Pin diagram and description |                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|-----|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin | Name                                 | Purpose                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 1   | GND                                  | Ground reference voltage, low level (0 V)                                                                                                                                                                                                                                                                                                                            |  |  |

| 2   | TRIG                                 | The OUT pin goes high and a timing interval starts when this input falls<br>below 1/2 of CTRL voltage (which is typically 1/3 Vcc, CTRL being<br>2/3 Vcc by default if CTRL is left open). In other words, OUT is high as<br>long as the trigger low. Output of the timer totally depends upon the<br>amplitude of the external trigger voltage applied to this pin. |  |  |

| 3   | OUT                                  | This output is driven to approximately 1.7 V below $+Vcc$ , or to GND.                                                                                                                                                                                                                                                                                               |  |  |

| 4   | RESET                                | A timing interval may be reset by driving this input to GND, but the timing does not begin again until RESET rises above approximately 0.7 volts. Overrides TRIG which overrides threshold.                                                                                                                                                                          |  |  |

| 5   | CTRL                                 | Provides "control" access to the internal voltage divider (by default, 2/3 Vcc).                                                                                                                                                                                                                                                                                     |  |  |

| 6   | THR                                  | The timing (OUT high) interval ends when the voltage at threshold is greater than that at CTRL (2/3 Vcc if CTRL is open).                                                                                                                                                                                                                                            |  |  |

| 7   | DIS                                  | Open collector output which may discharge a capacitor between intervals. In phase with output.                                                                                                                                                                                                                                                                       |  |  |

| 8   | Vcc                                  | Positive supply voltage, which is usually between 3 and 15 V depending on the variation.                                                                                                                                                                                                                                                                             |  |  |

## Some important features of the 555 timer:

555 timer is used in almost every electronic circuit today. For a 555 timer working as a <u>flip</u> <u>flop</u> or as a multi-vibrator, it has a particular set of configurations. Some of the major features of the 555 timer would be,

- It operates from a wide range of power ranging from +5 Volts to +18 Volts supply voltage.

- Sinking or sourcing 200 mA of load current.

- The external components should be selected properly so that the timing intervals can be made into several minutes along with the frequencies exceeding several hundred kilohertz.

- The output of a 555 timer can drive transistor-transistor logic (TTL) due to its high current output.

- It has a temperature stability of 50 parts per million (ppm) per degree Celsius change in temperature which is equivalent to 0.005 %/ °C.

- The duty cycle of the timer is adjustable.

- Also, the maximum power dissipation per package is 600 mW and its trigger and reset input has logic compatibility.

## 555 timer working:

The 555 generally operates in 3 modes: A-stable, Mono-stable, Bi-stable modes.

## Astable mode

This means there will be no stable level at the output. So the output will be swinging between high and low. This character of unstable output is used as a clock or square wave output for many applications.

## Mono-stable mode

This configuration consists of one stable and one unstable state. The stable state can be chosen either high or low by the user. If the stable output is set at high (1), the output of the timer is high (1). At the application of an interrupt, the timer output turns low (0). Since the low state is unstable it goes to high (1) automatically after the interrupt passes. Similar is the case for a low stable <u>monostable mode</u>.

## **Bi-stable mode**

In bistable mode, both the output states are stable. At each interrupt, the output changes from low (0) to high (1) and vice versa, and stays there. For example, if we have a high (1) output, it will go low (0) once it receives an interrupt and stays low (0) till the next interrupt changes the status.

## <u>Experiment –1</u>

## **Measurements of OP-AMP parameters, Voltage follower**

## **Measurements of OP-AMP parameters**

## <u>Aim:</u>

To measure the parameters of op-amp such as Input bias current, Input offset current, Input and Output offset voltage and Slew rate

## **Equipments/ Components Required**:

#### **Components:**

| Name      | Specifications/ Range | Quantity |

|-----------|-----------------------|----------|

| Op-amp    | μA741C                | 1        |

| Resistor  | 100Ω, ¼ W             | 2        |

|           | 10k, ¼ W              | 2        |

|           | 100k, ¼ W             | 1        |

| Capacitor | 0.01µF                | 2        |

## **Equipments:**

| Name               | Specifications/ Range | Quantity |

|--------------------|-----------------------|----------|

| IC Trainer board   |                       | 1        |

| Digital ammeter    | 0-200µA/200mA         | 1        |

| Digital voltmeter  | 0-2V/20V              | 1        |

| Function generator | 0-20MHz.              | 1        |

| Dual trace CRO     | 0-200MHz              | 1        |

| DC Power supply    |                       | 1        |

## Theory:

The  $\mu$ A741 device is a general-purpose operational Short-Circuit Protection amplifier featuring offset-voltage null capability.

**Input bias current:** The inverting and non-inverting terminals of an op-amp are actually two base terminals of transistors of a differential amplifier. In an ideal op-amp it is supported that no current flows through these terminals. However, practically a small amount of current flows through these terminals which is on the order of nA (typical and maximum values are 80 and 1500nA) in bipolar op-amps and pA for FET op-amps.

Input bias current is defined as the average of the currents entering into the inverting and noninverting terminals of an op-amp. To compensate for bias currents a compensating resistor  $R_{comp}$  is used. Value of  $R_{comp}$  is parallel combination of the resistors connected to the inverting terminal.

## Input bias current $I_B = (I_{B1}+I_{B2}) / 2$

where  $I_{B1}$  and  $I_{B2}$  are the base bias currents of the op-amp.

**Input offset current:** Input offset current is defined as the algebraic difference between the currents into the inverting and non-inverting terminals.

$$Ios = |I_{B1} - I_{B2}|$$

where  $I_{B1}$  and  $I_{B2}$  are the base bias currents of the op-amp. The bias currents IB1 and IB2 will not be equal in an op-amp.

Typical and maximum values of input offset current are 20nA and 200nA, respectively.

**Input offset voltage:** Even if the input voltage is zero, output voltage may not be zero. This is because of the circuit imbalances inside the op-amp. In order to compensate this, a small voltage should be applied between the input terminals. Input offset voltage is defined as the voltage that must be applied between the input terminals of an op-amp to nullify the output voltage. Typical and maximum values of input offset voltage are 2mV and 6mV, respectively.

<u>Slew rate</u>: Slew rate is the rate of rise of output voltage. It is the measure of fastness of opamp. It is expressed in  $V/\mu$ sec. If the slope requirements of the output voltage of the op-amp are greater than the slew rate, distortion occurs. Slew rate is measured by applying a step input voltage.

**Output offset voltage:** The voltage existing at the output when inputs are zero due to input offset voltage & bias current is called output offset voltage. Ideally it is zero when both input op-amp zero. It is only produced due to input offset voltage and bias current.

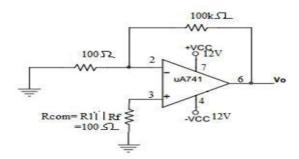

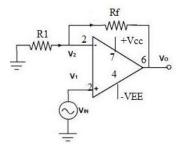

## **<u>Circuit Diagram</u>**: Measurement of Input and Output offset voltage

Fig.1.1: Circuit Diagram to measure input and output offset voltage

## Procedure:-

- 1. Connect the circuit as shown in Fig.1.1

- 2. Measure Output voltage i.e; Output offset voltage  $(V_{00})$ .

- 3. Calculated Input offset voltage from Vio = Voo / (1+Rf/R1)

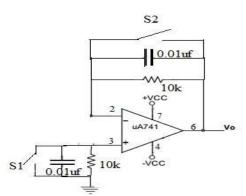

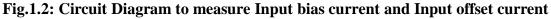

## **<u>Circuit Diagram</u>**: Measurement of Input bias current and Input offset current

## Procedure:-

- 1. Connect the circuit as shown in Fig.1.2.

- 2. Close the switch S1 and measure Output voltage.

- 3. Using the value of output voltage, calculate  $I_{B2}$

- 3. Now Close the switch S2 and measure Output voltage.

- 4. Using the value of output voltage, calculate  $I_{B1}$

- 5. Using the values of IB1 & IB2, Calculate Input bias current and Input offset current using

$I_{B} = |I_{B1} + I_{B2}|/2; \qquad Iio = |I_{B1}| - |I_{B2}|$

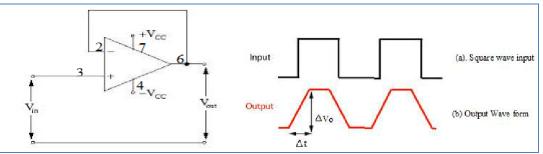

## **<u>Circuit Diagram</u>**: Measurement of slew rate

Fig.1.3: Circuit Diagram to measure slew rate

## **Procedure:-**

1. Connect unity gain amplifier circuit as shown in Fig. 1.3

- 2. Apply Square wave as input having magnitude 1 V (p-p) and frequency 1 KHz

- 3. Observe Output waveform by varying freq of input from 1 kHz to higher value

- 4. Slew rate is calculated using Slew Rate =  $\Delta Vo/\Delta t$

## **Observations & Calculations:**

1. Voo=.....

Vio = Voo / (1 + Rf/R1)

2. Vo<sub>2</sub>=.....

$I_{B2}=Vo/10K$

Vo1=.....

$I_{B1} = Vo_1/10K.$

$I_B = |I_{B1} + I_{B2}|/2$

$Iio=\mid \!\! I_{B1}\mid - \mid \!\! I_{B2}\mid$

3. ΔVo... ..V Δt=...μ sec Slew rate=...

## **Result:**

The input bias current, input offset current, input offset voltage and slew rate of the op-amp

were determined. 4. Input offset voltage = .....mV Input bias current = .....A Input offset current = .....A Slew rate = .....V/µs.

## **EXPERIMENT-2**

## Inverting and non- Inverting amplifiers using Op-Amp

#### <u>Aim:-</u>

- 1. To design an inverting amplifier using op-amp with gain of -10.

- 2. To design a non-inverting amplifier using op-amp with gain of 11.

- 3. To realize a voltage follower using op-amp.

## **Equipments / Components Required**:

#### **Components:**

| Name     | Specifications/ Range | Quantity |  |

|----------|-----------------------|----------|--|

| Op-amp   | μA741C                | 1        |  |

| Resistor | $100\Omega$           | 2        |  |

|          | 10k Ω                 | 1        |  |

|          | 100k Ω                | 1        |  |

## **Equipment:**

| Name               | Specifications/ Range | Quantity |

|--------------------|-----------------------|----------|

| IC Trainer board   |                       | 1        |

| Function generator | 0-20MHz.              | 1        |

| Dual trace CRO     | 0-200MHz              | 1        |

| DC Power supply    |                       |          |

## **THEORY:**

## **INVERTING AMPLIFIER:**

In this **Inverting Amplifier** circuit the operational amplifier is connected with feedback to produce a closed loop operation. When dealing with operational amplifiers there are two very important rules to remember about inverting amplifiers, these are: "No current flows into the input terminal" and that "V1 always equals V2". However, in real world op-amp circuits both of these rules are slightly broken.

This is because the junction of the input and feedback signal (X) is at the same potential as the positive (+) input which is at zero volts or ground then, the junction is a **"Virtual Earth"**. Because of this virtual earth node the input resistance of the amplifier is equal to the value of the input resistor, Rin and the closed loop gain of the inverting amplifier can be set by the ratio of the two external resistors.

We said above that there are two very important rules to remember about **Inverting Amplifiers** or any operational amplifier for that matter and these are.

- No Current Flows into the Input Terminals

- The Differential Input Voltage is Zero as V1 = V2 = 0 (Virtual Earth)

## Design Of Inverting Amplifier:-

The gain of an inverting amplifier is given by  $A_v = V_o/V_{in} = -R_f/R_1$

Given that  $A_v = -10$

Assume that  $R_1=10K\Omega$

Therefore,  $R_f = A_v R_1 = -10 \ x \ 10 \ x \ 10^3 = 100 K\Omega$

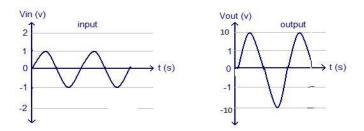

**Fig.2.1: Inverting Amplifier**

## Procedure:-

- 1. Connect the circuit as per the circuit diagram shown in Fig.2.1

- 2. Apply sine wave as input with the magnitude of 1V (p-p) and frequency 1 KHz

- 3. Observe the output wave and note down the amplitude of output voltage.

- 4. Compare the practical value of V<sub>o</sub> with its theoretical value.

- 5. Calculate the gain of the amplifier using  $A_v = -V_o / V_i$ .

## **Observations:**

$V_i = 1 V (p-p), f_i = 1 KHz$

| Sl. No. | Output voltage V <sub>o</sub> (Volts) | Output voltage V <sub>0</sub> (Volts) | Gain |

|---------|---------------------------------------|---------------------------------------|------|

|         | Practical                             | Theoretical                           |      |

| 1       |                                       |                                       |      |

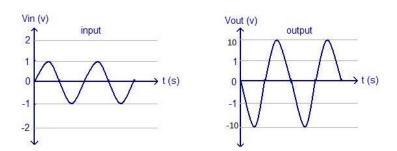

Fig. 2.2: Input and Output wave forms of an Inverting amplifier

## Non- Inverting Amplifier:-

In this configuration, the input voltage signal,  $(V_{IN})$  is applied directly to the non-inverting (+) input terminal which means that the output gain of the amplifier becomes "Positive" in value in contrast to the "Inverting Amplifier" circuit whose output gain is negative in value. The result of this is that the output signal is "in-phase" with the input signal.

Feedback control of the non-inverting operational amplifier is achieved by applying a small part of the output voltage signal back to the inverting (-) input terminal via a Rf – R2 voltage divider network, again producing negative feedback. This closed-loop configuration produces a non-inverting amplifier circuit with very good stability, very high input impedance, R<sub>in</sub> approaching infinity, as no current flows into the positive input terminal, (ideal conditions) and low output impedance, Rout.

## **Design Of Non-Inverting Amplifier:-**

Gain of an inverting Amplifier is given by  $A_v = V_o / V_{in} = 1 + R_f / R_1$

Given that  $A_v = 11$

Assume that  $R_1=10K\Omega$

Therefore,  $R_f = (A_v-1) \times R_1 = (11-1) \times 10 \times 10^3 = 100 \text{K}\Omega$

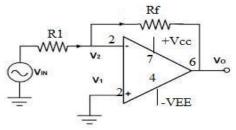

Fig. 2.3: Non-Inverting Amplifier

## Procedure:-

- 1. Connect the circuit as per the circuit diagram shown in Fig.2.3

- 2. Apply sine wave as input with a magnitude of 1 V(p-p) and frequency 1 KHz.

- 3. Observe the output wave and note down the amplitude of output voltage.

- 4. Compare the practical value of  $V_0$  with its theoretical value.

- 5. Calculate the gain of the amplifier using  $A_v = V_o / V_{in}$

## **Observations:**

$V_i = 1 V (p-p), f_i = 1 KHz$

| Sl. No. | Output voltage V <sub>o</sub> (Volts) | Output voltage V <sub>0</sub> (Volts) | Gain |

|---------|---------------------------------------|---------------------------------------|------|

|         | Practical                             | Theoretical                           |      |

| 1       |                                       |                                       |      |

Fig. 2.4: Input and Output wave forms of Non- Inverting amplifier

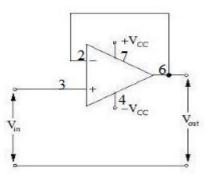

## **Voltage Follower :-**

If the feedback resistor, Rf is made equal to zero, (Rf = 0), and resistor R1 equal to infinity,  $(R1 = \infty)$ , then the circuit would have a fixed gain of "1" as all the output voltage would be present on the inverting input terminal (negative feedback). This would then produce a special type of the non-inverting amplifier circuit called a **Voltage Follower**.

**Voltage follower** is an <u>Op-amp</u> circuit whose output <u>voltage</u> straight away follows the input voltage. That is output voltage is equivalent to the input voltage. Op-amp circuit does not provide any amplification. Thus, voltage gain is equal to 1. They are similar to discrete emitter follower.

The other names of voltage follower are Isolation Amplifier, Buffer Amplifier, and Unity-Gain Amplifier. The voltage follower provides no attenuation or no amplification but only buffering. This circuit has an advantageous characteristic of very high input impedance.

Fig. 2.5: Voltage Follower

## Procedure:-

- 1. Connect the circuit as per the circuit diagram shown in Fig.2.5

- 2. Apply sine wave as input with a magnitude of 1 V(p-p) and frequency 1 KHz.

- 3. Observe the output wave and note down the amplitude of output voltage.

- 4. Compare the practical value of  $V_o$  with its theoretical value.

- 5. Calculate the gain of the amplifier using  $A_v = V_o / V_{in}$

Fig. 2.5: Input and Output wave forms of Voltage follower

## **Result:**

Studied the operation of the basic applications of op-amp and Gain of the Inverting amplifier, Non-Inverting amplifier and Voltage follower were determined.

Gain of the Inverting amplifier=.....

Gain of the Non-Inverting amplifier=.....

Gain of the Voltage follower=.....

#### **Review Questions:**

- 1. What is input bias current?

- 2. Why do we use  $R_{comp}$  resistor?

- 3. What is thermal drift?

- 4. Why is IC741 op-amp not used for high frequency applications?

- 5. What is unity gain circuit?

- 6. Which amplifier acts as a Subtractor?

- 7. Draw the circuit diagram of 3 input adder.

- 8. Draw an op- amp circuit whose output Vo is V1+V2-V3-V4.

## Experiment 3

## **Integrator and Differentiator Using Op-Amp**

#### Aim :-

- 1. Design a differentiator to differentiate an input signal with fmax= 1 kHz.

- 2. Design an integrator circuit to properly process input waveform upto 1KHz.

## **Equipments/ Components Required**:

#### **Components:**

| Name      | Specifications/ Range | Quantity |  |

|-----------|-----------------------|----------|--|

| Op-amp    | μA741C                | 1        |  |

| Resistor  | 1KΩ, ¼ W              | 3        |  |

|           | 1.5KΩ , ¼ W           | 2        |  |

|           | 15KΩ, ¼ W             | 1        |  |

|           | 10k, ¼ W              | 4        |  |

|           | 150Ω, ¼ W             | 1        |  |

|           | 100k, ¼ W             | 1        |  |

| Capacitor | 0.01uf                | 1        |  |

|           | 0.1uf                 | 1        |  |

#### Equipment

| Name               | Specifications/ Range | Quantity |

|--------------------|-----------------------|----------|

| IC Trainer board   |                       | 1        |

| Function generator | 0-20MHz.              | 1        |

| Dual trace CRO     | 0-200MHz              | 1        |

| DC Power supply    |                       | 1        |

## Integrator:-

Operational amplifier can be configured to perform calculus operations such as differentiation and integration. In an integrating circuit, the output is the integration of the input voltage with respect to time.

A passive integrator is a circuit which does not use any active devices like op-amps or transistors.

An integrator circuit which consists of active devices is called an Active integrator. An active integrator provides a much lower output resistance and higher output voltage than is possible with a simple RC circuit.

Op-amp integrating circuit is inverting amplifier, with appropriately placed capacitor. Integrator circuits are usually designed to produce a triangular wave output from a square wave input.

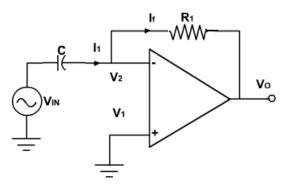

Integrating circuits have frequency limitations while operating on sine wave input signals. The circuit in fig 3.1 is an integrator, which is also a low-pass filter with a time constant=R<sub>1</sub>C. When a voltage, V<sub>in</sub> is firstly applied to the input of an integrating amplifier, the uncharged capacitor C has very little resistance and acts a bit like a short circuit (voltage follower circuit) giving an overall gain of less than 1, thus resulting in zero output. As the feedback capacitor C begins to charge up, its reactance X<sub>c</sub> decreases and the ratio of Z<sub>f</sub>/R<sub>1</sub> increases producing an output voltage that continues to increase until the capacitor is fully charged. At this point the ratio of feedback capacitor to input resistor (Z<sub>f</sub>/R<sub>1</sub>) is infinite resulting in infinite gain and the output of the amplifier goes into saturation. (Saturation is when the output voltage of the amplifier swings heavily to one voltage supply rail or the other with no control in between). The circuit design generate triangular wave providing square wave as input to the integrator. Hence, the integrator circuit generates integral output with respect to the input waveform.

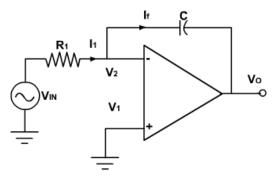

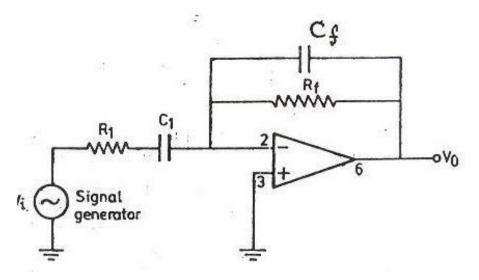

Fig.3.1: Integrator using Op-amp

Integrator has wide applications in Analog computers used for solving differential equations in simulation arrangements, A/D Converters, Signal wave shaping and Function Generators **Design of Integrator**:-

The frequency responses of the practical and ideal integrator are shown in the above figure. For both circuits, the crossover frequency  $f_b$ , at which the gain is 0 dB, is given by:

$$f_b=1/2\pi R_1C_f$$

The 3 dB <u>c</u>ut-off frequency  $f_a$  of the practical circuit is given by:

$$f_a=1/2\pi R_f C_f$$

Choose  $f_b{=}10f_a$  ,  $C_f{=}0.01\mu f$

ICA LAB MANUAL(ECE)

We know that  $f_b=1/2\pi R_1C_f=1$ KHz

## Therefore, R1 = $15.9K \approx 16K\Omega$

Now,  $f_a = f_b / 10 = 100 \text{Hz}$

$f_a = 1/2\pi R_f C_f => R_f = 160 K \Omega$

Therefore,  $\mathbf{R}_{comp} = \mathbf{R}\mathbf{1} | | \mathbf{R}\mathbf{f} \approx \mathbf{15}\mathbf{K}\Omega$

## **Circuit Diagram:**

Fig.3.2: Integrator using Op-amp

## Procedure (Integrator):-

- 1. Connect the circuit as per the circuit diagram shown Fig.3.2.

- 2. Switch ON the power supply.

3. Apply sine wave at the input terminals of the circuit using function Generator.

4. Connect channel-1 of CRO at the input terminals and channel-2 at the output terminals.

5. Observe the output of the circuit on the CRO which is a cosine wave (900 phase shifted from the sine wave input) and note down the position, the amplitude and the time period of  $V_{in} \& V_{o}$ .

6. Now apply the square wave as input signal.

7. Observe the output of the circuit on the CRO which is a triangular wave and note down the position, the amplitude and the time period of  $V_{in} \& V_{o}$ .

8. Plot the output voltages corresponding to sine and square wave inputs.

#### **Expected Waveforms Of Integrator:**

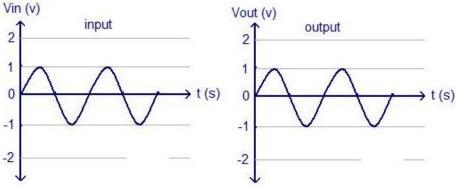

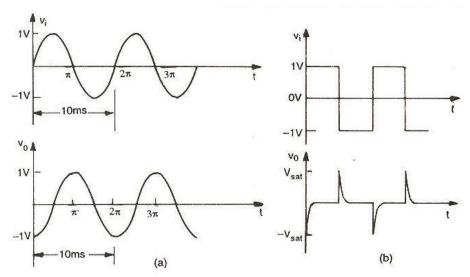

Fig.3.3: Expected Input and Output waveforms of Integrator

#### **Differentiator:-**

The basic Differentiator Amplifier circuit is the exact opposite to that of the Integrator operational amplifier circuit that we saw in the previous experiment. Here, the position of the capacitor and resistor have been reversed and now the Capacitor, C is connected to the input terminal of the inverting amplifier while the Resistor,  $R_1$  forms the negative feedback element across the operational amplifier. This circuit performs the mathematical operation of Differentiation that is it produces a voltage output which is proportional to the input voltage's rate-of-change and the current flowing through the capacitor. Or in other words the output voltage is a scaled version of the derivative of the input voltage. The capacitor blocks any DC content only allowing AC type signals to pass through and whose frequency is dependent on the rate of change of the input signal. At low frequencies the reactance of the capacitor is "High" resulting in a low gain ( $R_1/X_c$ ) and low output voltage from the op-amp.

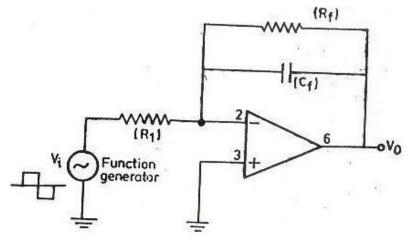

Fig.3.4: Differentiator using Op-amp

As the name suggests, the circuit performs the mathematical operation of differentiation, i.e. the output voltage is the derivative of the input voltage.

$$\mathbf{V}_{\mathbf{o}} = -\mathbf{R}_{\mathbf{f}}\mathbf{C}_{1} \frac{dV_{im}}{dt}$$

Both the stability and the high-frequency noise problems can be corrected by the addition of two components:  $R_1$  and  $C_f$ , **as shown in the circuit diagram**. This circuit is a practical differentiator. The input signal will be differentiated properly if the time period T of the input signal is larger than or equal to  $R_fC_1$ . That is,  $T \ge R_fC_1$

Differentiator can be designed by implementing the following steps.

1. Select fa equal to the highest frequency of the input signal to be differentiated. Then, assuming a value of  $C_1 < 1 \ \mu$ F, calculate the value of  $R_f$

Calculate the values of  $R_1$  and  $C_f$  so that  $R_1C_1=R_fC_f$ .

Differentiator has wide applications in Monostable Multivibrator, Signal wave shaping and Function Generators.

## Design:-

Given that  $f_b = fmax = 1 \text{ kHz}$

We know that  $f_b = 1/2\pi R_1 C_f$

Assuming  $C_1 = 0.1 \mu f$ , We get,  $R_f = 1.5 K\Omega$

$f_a = 1/2\pi R_1 C_1 {=} 10 {f_b}$

fa=10KHz

$R1=159\Omega\approx 150\Omega$

We know that  $R_1C_1 = R_fC_f$

Therefore,  $C_f = R_1C_1 / R_f = 0.01 \mu f$

## **Circuit Diagram:**

Fig.3.5: Differentiator using Op-amp

#### Procedure (Differentiator):-

1. Connect the components/equipment as shown in the circuit diagram.

- 2. Switch ON the power supply.

- 3. Apply sine wave at the input terminals of the circuit using function Generator.

- 4. Connect channel-1 of CRO at the input terminals and channel-2 at the output terminals.

5. Observe the output of the circuit on the CRO which is a cosine wave (900 phase shifted from the sine wave input) and note down the position, the amplitude and the time period of Vin & Vo.

6. Now apply the square wave as input signal.

7. Observe the output of the circuit on the CRO which is a spike wave and note down the position, the amplitude and the time period of Vin & Vo.

8. Plot the output voltages corresponding to sine and square wave inputs.

#### **EXPECTED WAVEFORMS OF DIFFERENTIATOR:--**

Fig.3.6: Expected Input and Output waveforms of Differentiator

## **Result:-**

#### **Review Questions:-**

- 1. What is an Integrator?

- 2. Draw the circuit of the Integrator using op-amp IC741.

- 3. Write down the expression for Vo of an Integrator.

- 4. Draw the frequency response of the Integrator and explain.

- 5. Draw the output waveform of the Integrator when the input is a Square wave.

- 6. What is the purpose behind the connection of Rf in the feedback path of Integrator?

- 7. What are the applications of Integrator?

- 8. Why  $R_{comp}$  is used in both Integrator and Differentiator circuits?

- 9. What is a Differentiator?

- 10. Draw the circuit of the Differentiator using op-amp IC741.

- 11. Write down the expression for  $V_o$  of a Differentiator.

- 12. Draw the output waveform of the Differentiator when the input is a Sine wave.

- 13. Why R1 and Cf are connected in the circuit of the Differentiator?

- 14. What are the applications of Differentiator?

## Experiment 4

## **ACTIVE FILTERS**

**Aim:-** To design a first order low pass, high pass filter at a cut off frequency of 1KHz with a pass band gain at 2.

To design a first order Butterworth narrow band pass filter at a cut off frequency of 10 KHz with Q=10.

## **Equipments/ Components Required:**

## **Components:**

| Name      | Specifications/ Range | Quantity |

|-----------|-----------------------|----------|

| Op-amp    | μA741C                | 1        |

| Resistor  | 15KΩ<br>1KΩ           | 1        |

|           | 10kΩ<br>100Ω          | 3        |

| Capacitor | -0.01uf,1nf           | 1        |

## **Equipments:**

| Name               | Specifications/ Range | Quantity |

|--------------------|-----------------------|----------|

| IC Trainer board   |                       | 1        |

| Function generator | 0-20MHz.              | 1        |

| Dual trace CRO     | 0-200MHz              | 1        |

| DC Power supply    |                       |          |

## Theory:-

In the RC Passive Filter, a basic first-order filter circuits, such as the low pass and the high pass filters, can be made using just a single resistor in series with a non-polarized capacitor connected across a sinusoidal input signal.

It is also noticed that the main disadvantage of passive filters is that the amplitude of the output signal is less than that of the input signal, ie, the gain is never greater than unity and that the load impedance affects the filters characteristics.

With passive filter circuits containing multiple stages, this loss in signal amplitude called "Attenuation" can become quiet severe. One way of restoring or controlling this loss of signal is by using amplification through the use of **Active Filters**.

As their name implies, **Active Filters** contain active components such as operational amplifiers, transistors or FET's within their circuit design. They draw their power from an external power source and use it to boost or amplify the output signal.

Filter amplification can also be used to either shape or alter the frequency response of the filter circuit by producing a more selective output response, making the output bandwidth of the filter narrower or even wider. Then the main difference between a "passive filter" and an "active filter" is amplification.

An active filter generally uses an operational amplifier (op-amp) within its design and in the Operational Amplifier tutorial we saw that an Op-amp has high input impedance, a low output impedance and a voltage gain determined by the resistor network within its feedback loop.

Unlike a passive high pass filter which has in theory an infinite high frequency response, the maximum frequency response of an active filter is limited to the Gain/Bandwidth product (or open loop gain) of the operational amplifier being used. Still, active filters are generally much easier to design than passive filters, they produce good performance characteristics, very good accuracy with a steep roll-off and low noise when used with a good circuit design.

## Active Low Pass Filter

The most common and easily understood active filter is the **Active Low Pass Filter**. Its principle of operation and frequency response is exactly the same as those for the previously seen passive filter, the only difference this time is that it uses an op-amp for amplification and gain control. The simplest form of a low pass active filter is to connect an inverting or non-inverting amplifier, the same as those discussed in the Op-amp tutorial, to the basic RC low pass filter circuit as shown.

This first-order low pass active filter consists simply of a passive RC filter stage providing a low frequency path to the input of a non-inverting operational amplifier. The amplifier is configured as a voltage-follower (Buffer) giving it a DC gain of one, Av = +1 or unity gain as opposed to the passive RC filter which has a DC gain of less than unity.

The advantage of this configuration is that the op-amps high input impedance prevents excessive loading on the filters output while its low output impedance prevents the filters cutoff frequency point from being affected by changes in the impedance of the load.

While this configuration provides good stability to the filter, its main disadvantage is that it has no voltage gain above one. However, although the voltage gain is unity the power gain is very high as its output impedance is much lower than its input impedance. If a voltage gain greater than one is required we can use the following filter circuit.

These Active Filters are most extensively used in the field of communications and signal processing. They are employed in one form or another in almost all sophisticated electronic systems such as Radio, Television, Telephone, Radar, Space Satellites, and Bio-Medical

Equipment. Active Filters employ transistors or Op - Amps in addition to that of resistors and capacitors. Active filters have the following advantages over passive filters. (1) Flexible gain and frequency adjustment. (2) No loading problem (because of high input impedance and low output impedance) and (3) Active filters are more economical than passive filters.

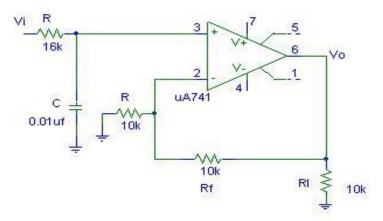

## Design of First Order Low Pass Filter:-

Cut off frequency is given as fc=1 kHz

Assume that C=0.01uf

Therefore,  $\mathbf{R} = 1 / 2\pi f_c \mathbf{C} = \mathbf{16}\mathbf{K}\mathbf{\Omega}$

Given that Pass band gain, A = 2

We know that  $A=1+R_{\rm f}\,/\,R_1$

Therefore,  $2 = 1 + R_f / R_1$

Therefore,  $R_f = R_1 = 10K\Omega$

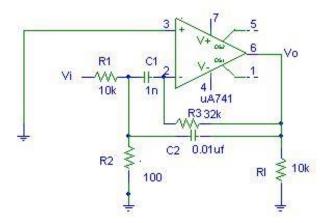

Circuit Diagram of First Order Low Pass Filter:-

Fig.4.1: First Order Low Pass Filter

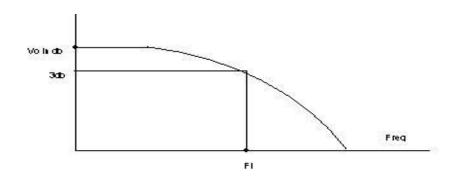

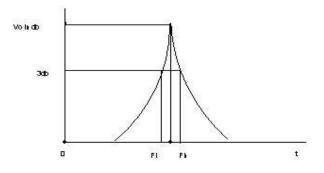

**Expected Plot of Frequency Response:-**

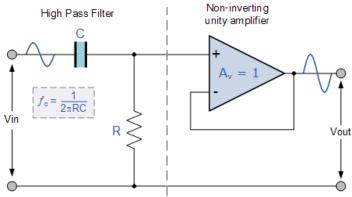

## First Order High Pass Filter:-

The basic operation of an **Active High Pass Filter** (HPF) is the same as RC passive high pass filter circuit, except an operational amplifier or included within its design providing amplification and gain control.

Like the active low pass filter circuit, the simplest form of an *active high pass filter* is to connect a standard inverting or non-inverting operational amplifier to the basic RC high pass passive filter circuit as shown in Fig.4.3.

## **First Order High Pass Filter**

Fig.4.3: First Order High Pass Filter

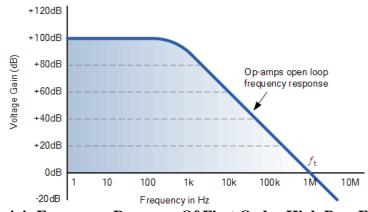

Technically, there is no such thing as an **active high pass filter**. Unlike Passive High Pass Filters which have an "infinite" frequency response, the maximum pass band frequency response of an active high pass filter is limited by the open-loop characteristics or bandwidth of the operational amplifier being used, making them appear as if they are band pass filters with a high frequency cut-off determined by the selection of op-amp and gain.

In the Operational Amplifier tutorial we saw that the maximum frequency response of an opamp is limited to the Gain/Bandwidth product or open loop voltage gain  $(A_V)$  of the operational amplifier being used giving it a bandwidth limitation, where the closed loop response of the op amp intersects the open loop response.

A commonly available operational amplifier such as the uA741 has a typical "open-loop" (without any feedback) DC voltage gain of about 100dB maximum reducing at a roll off rate of -20dB/Decade (-6db/Octave) as the input frequency increases. The gain of the uA741 reduces until it reaches unity gain, (0dB) or its "transition frequency" (ft) which is about 1MHz. This causes the op-amp to have a frequency response curve very similar to that of a first-order low pass filter and this is shown in Fig. .

Fig.4.4: Frequency Response Of First Order High Pass Filer

## **Active High Pass Filter**

A first-order (single-pole) Active High Pass Filter as its name implies, attenuates low frequencies and passes high frequency signals. It consists simply of a passive filter section followed by a non-inverting operational amplifier. The frequency response of the circuit is the same as that of the passive filter, except that the amplitude of the signal is increased by the gain of the amplifier and for a non-inverting amplifier the value of the pass band voltage gain is given as 1 + R2/R1, the same as for the low pass filter circuit.

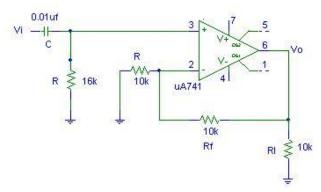

## **Design of First Order High Pass Filter**

Given that Cut off frequency,  $f_c = 1 \text{ kHz}$ Assuming C=0.01µF, Therefore R=  $1/2\pi f_c C = 16K\Omega$ Given that Pass band gain, A = 2 We know that Pass band gain, A=1 + R<sub>f</sub> / R<sub>1</sub> Therefore, 2 = 1+ R<sub>f</sub> / R<sub>1</sub> Therefore, R<sub>f</sub> = R<sub>1</sub> = 10KΩ

Circuit Diagram of First Order High Pass Filter:-

Fig.4.5: Circuit Diagram Of First Order High Pass Filter

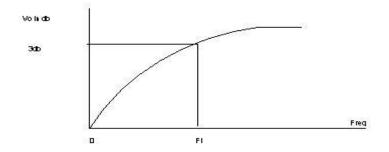

Expected Plot of Frequency Response Of First Order High Pass Filter:-

Fig.4.6: Frequency Response Of First Order High Pass Filter

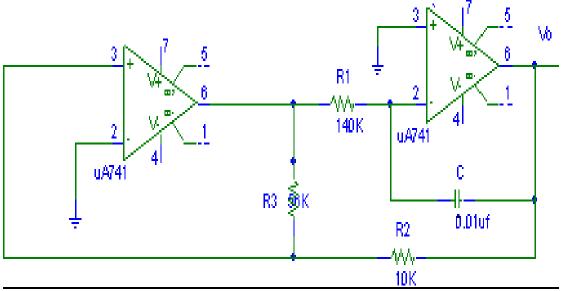

Design of Narrow Band Pass Filter:-

Given that Pass Band gain, A = 10,  $f_c=10$  KHz and Q=10

Assuming that C=0.01 $\mu$ F, R<sub>1</sub> = Q/2 $\pi$ fc.C.A =1.6 K $\Omega$

$$R_2 = Q / 2 \pi$$

fc. C.  $(2Q^2-A) = 100\Omega$

R3 = Q / 2  $\pi$  fc. C = 32K $\Omega$

# Circuit Diagram of Narrow Band Pass Filter:-

Fig.4.7:Circuit Diagram Of Narrow Band Pass Filter

# Procedure:-

- 1. Connect the circuit as shown in figure.

- 2. Adjust  $V_{in} = 4v$  (P-P) & keep it constant thought-out the experiment.

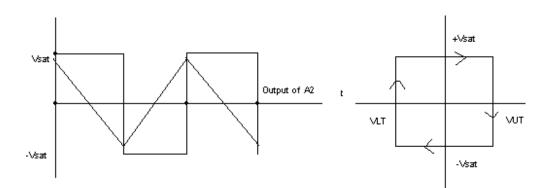

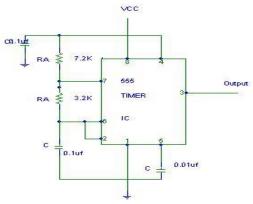

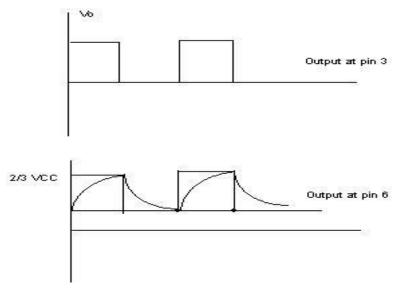

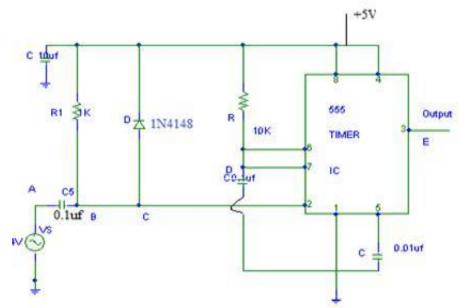

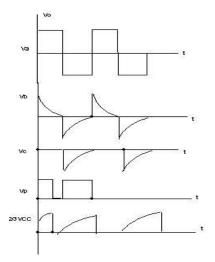

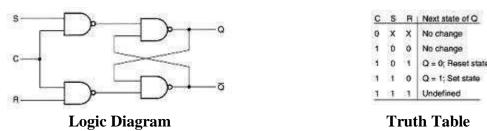

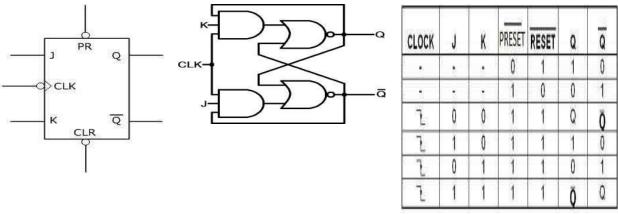

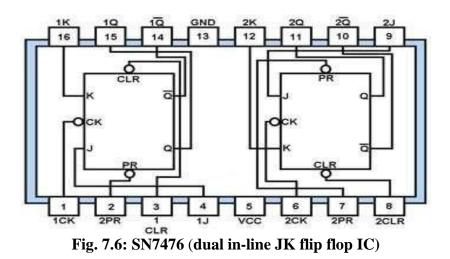

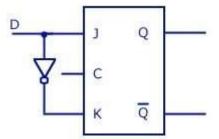

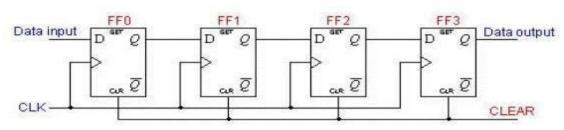

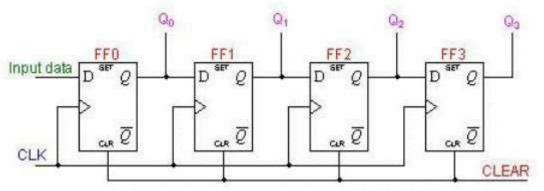

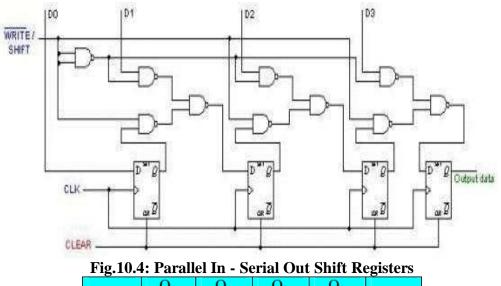

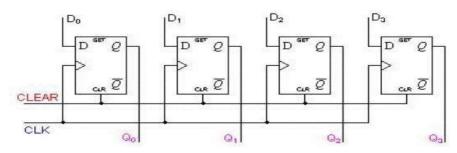

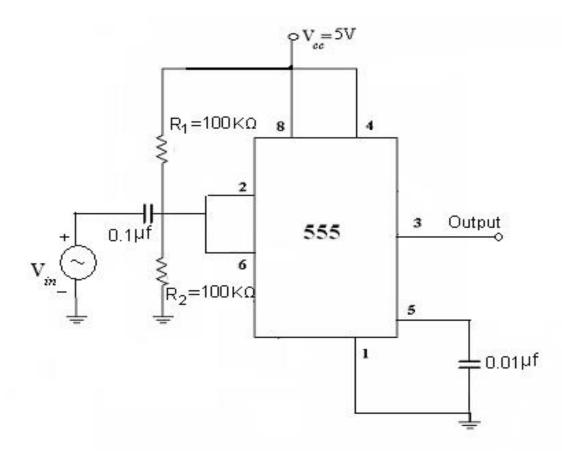

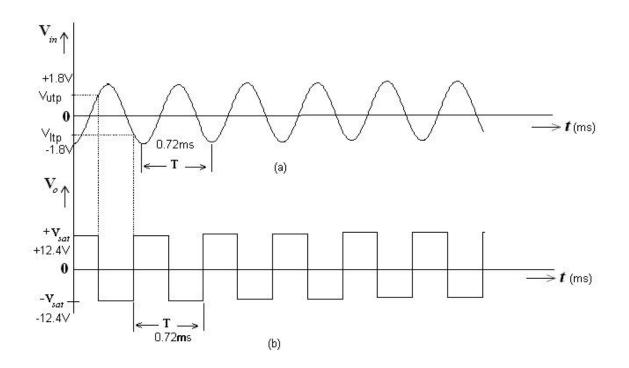

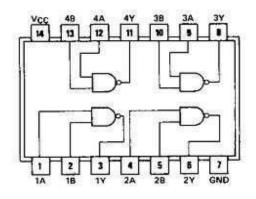

3. Vary the input frequency from 20Hz to 20 KHz & Note down peak to peak voltage across  $R_1$  using CRO.